Memory Systems

What are the registers used in DMA? Discuss DMA interfacing with processor.

- DMA stands for the Direct Memory Access.

- It is the mechanism of synchronizing the system or the data flow among the input and output devices.

- DMA uses a set of 4 operational registers and two supporting registers which are all 24-bit registers.

Namely1. DMA Source Address Register (DSR): It contains the source address for the next access in the same channel as every channel has its unique address.

2. DMA Destination Address Register (DDR): It contains the address of the destination for the transfer in same channel.

3. DMA Counter (DCO): It keeps record of the number of data transfers that are carried out in the channel.

4. DMA Control Register (DCR): It access the operations that are carried out in the channel.

The 2 supporting registers are:DMA Offset Register (DOR): It consists of the offset value that is used by some address generation modes.

DMA Status Register (DSTR): Its the only “read-only” register that provides the status of all the channels.

DMA interfacing with ProcessorFollowing steps explain the DMA interfacing with the processor:

- Step 1: The device that wish to perform DMA gives the processors bus request signal.

- Step 2: Processor acknowledges the current bus cycle and then provides the bus grant signal to the device.

- Step 3: The device after this gives the bus grant acknowledgement signal.

- Step 4: The processor finds the change in the state of bus grant acknowledgement signal and starts listening to the data and address bus for the DMA activity.

- Step 5: The DMA device carries out the transfer from the source address to destination address.

- Step 6: During transfer, the processor monitors the addresses on the bus and checks if any location has been modified during this. If the processor detects a stored address on the bus, it can either invalidate that address or update the internal memory with that address.

- Step 7: After the DMA operation is complete, the device releases the bus by giving the bus release signal.

- Step 8: The processor acknowledges this signal and resumes its bus cycles from the point where it left.

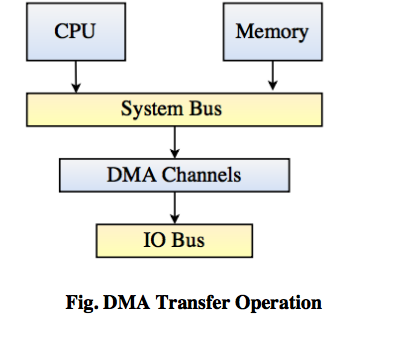

What is DMA? Draw the block diagram of DMA transfer operation.

- DMA stands for direct memory access.

- It helps in speeding up the execution process by controlling the input/output data transfer without bringing the CPU in action.

- The task is completed by using the DMA Controller.

For direct memory access- The device must be assigned to a DMA channel.

- Every channel needs two lines in order to function. One is for the DMA controller and other is for the CPU to ensure that DMA controller is able to send data through the lines.

- It transfers the data without letting CPU to handle it and thus saves the CPU time as it can handle other operations in the meantime.

- The transfer operations in DMA can be performed in many ways. One of them is:

Bus-Master DMA Transfers- Describe the DMA attributes to ensure that the device is able to access the buffer.

- Allocate a DMA handle and resource for object.

- Start the DMA engine after programming it on device.

- Continue the bus master operation even after the transfer is completed.

- Perform any synchronization operation required.

- Free the DMA handle.

Diagram Explanation

Explanation- As can be seen in the diagram, the transfer being carried out using the DMA controller between the device and the memory without letting the CPU come into the picture. The read write operations are being carried put on the channels and the system bus is connecting each segment for the bus cycle.