1) Which factor/s is/are supposed to have the equal values at both phases of transmission and reception levels with an intimation of error-free serial communication?

a. Baud Rate

b. Number of data bits & stop bits

c. Status of Parity bits

d. All of the above

|

2) Which bits exhibit and signify the termination phase of the character transmission and reception in SCON special function register?

a. Control bits

b. Status bits

c. Both a & b

d. None of the above

|

3) Which two bits are supposed to be analyzed/tested for unity value (1) in SCON for the reception of byte in mode 1 serial communication?

a. RI & TI

b. REN & RB8

c. RI & REN

d. TI & RB8

|

4) What is the bit transmitting or receiving capability of mode 1 in serial communication?

a. 8 bits

b. 10 bits

c. 11 bits

d. 12 bits

|

5) Which pin in the shift register mode (Mode 0) of serial communication allow the data transmission as well as reception?

a. TXD

b. RXD

c. RB8

d. REN

|

6) How is the baud rate determined on the basis of system clock frequency (fsc) in accordance to mode '0' of serial communication?

a. (oscillator frequency) / 12

b. [2SMOD / 32] x (oscillator frequency) / [12 x (256 – (TH1)]

c. [2SMOD / 64] x (oscillator frequency)

d. 2SMOD/ 32 x (Timer 1 overflow rate)

|

7) Which serial modes possess the potential to support the multi-processor type of communication?

a. Modes 0 & 1

b. Modes 1 & 2

c. Modes 2 & 3

d. All of the above

|

8) How does it become possible for 9th bit to differentiate the address byte from the data byte during the data transmission process in multiprocessor communication?

a. By recognizing 9th bit as '1' for address byte & '0' for data byte

b. By recognizing 9th bit as '0' for address byte & '1' for data byte

c. By recognizing 9th bit as '1' for address as well as data bytes

d. By recognizing 9th bit as '0' for address as well as data bytes

|

Answer

Explanation

Related Ques

|

ANSWER: By recognizing 9th bit as '1' for address byte & '0' for data byte

Explanation:

No explanation is available for this question!

|

|

9) Which byte has the capability to interrupt the slave when SM2 bit is assigned to be '1' after the initialization process in the multiprocessor mode of communication?

a. Address byte

b. Data byte

c. Both a & b

d. None of the above

|

10) Which bits of opcode specify the type of registers to be used in the register addressing mode?

a. LSB

b. MSB

c. Both a & b

d. None of the above

|

11) Which base-register is preferred for address calculation of a byte that is to be accessed from program memory by base-register plus register-indirect addressing mode?

a. DPTR

b. PSW

c. PCON

d. All of the above

|

12) What does the symbol '#' represent in the instruction MOV A, #55H?

a. Direct datatype

b. Indirect datatype

c. Immediate datatype

d. Indexed datatype

|

13) How many single byte, two-byte and three-byte instructions are supported by MCS-51 from the overall instruction set?

a. 55 - single byte, 35 two-byte & 21 three-byte instructions

b. 50 - single byte, 30 two-byte & 31 three-byte instructions

c. 42 - single byte, 45 two-byte & 24 three-byte instructions

d. 45 - single byte, 45 two-byte & 17 three-byte instructions

|

Answer

Explanation

Related Ques

|

ANSWER: 45 - single byte, 45 two-byte & 17 three-byte instructions

Explanation:

No explanation is available for this question!

|

|

14) What kind of PSW flags remain unaffected by the data transfer instructions?

a. Auxillary Carry Flags

b. Overflow Flags

c. Parity Flags

d. All of the above

|

15) Which instruction should be adopted for moving an accumulator to the register from the below mentioned mnemonics?

a. MOV A, Rn

b. MOV A, @ Ri

c. MOV Rn, A

d. MOV direct, A

|

16) What does the instruction XCHD A, @Ri signify during the data transfer in the program execution?

a. Exchange of register with an accumulator

b. Exchange of direct byte with an accumulator

c. Exchange of indirect RAM with an accumulator

d. Exchange of low order digit indirect RAM with an accumulator

|

Answer

Explanation

Related Ques

|

ANSWER: Exchange of low order digit indirect RAM with an accumulator

Explanation:

No explanation is available for this question!

|

|

17) Which flag allow to carry out the signed as well as unsigned addition and subtraction operations?

a. CY

b. OV

c. AC

d. F0

|

18) How many bytes are supposed to get occupied while subtracting indirect RAM from an accumulator along with borrow under the execution of SUBB A, @Ri?

a. 1

b. 2

c. 3

d. 4

|

19) What can be the oscillator period for the multiplication operation of A & B in accordance to 16-bit product especially in B:A registers?

a. 12

b. 24

c. 36

d. 48

|

20) Which form of instructions also belong to the category of logical instructions in addition to bitwise logical instructions?

a. Single-operand instructions

b. Rotate instructions

c. Swap instructions

d. All of the above

|

21) Which rotate instruction/s has an ability to modify CY flag by moving the bit-7 & bit-0 respectively to an accumulator?

a. RR & RL

b. RLC & RRC

c. RR & RRC

d. RL & RLC

|

22) Which among the single operand instructions complement the accumulator without affecting any of the flags?

a. CLR

b. SETB

c. CPL

d. All of the above

|

23) Match the following

a. JC rel -------------------- 1. Jump if direct bit is set & clear bit

b. JNC rel ------------------ 2. Jump if direct bit is set

c. JB bit, rel --------------- 3. Jump if direct bit is not set

d. JBC bit, rel ------------ 4. Jump if carry is set

e. JNB bit, rel ------------- 5. Jump if carry is not set

a. A-3, B-2, C-1, D-4, E-5

b. A-5, B-2, C-4, D-1, E-3

c. A-5, B-4, C-3, D-2, E-1

d. A-4, B-5, C-2, D-1, E-3

|

24) What is the possible range of transfer control for 8-bit relative address especially in 2's complement form with respect to the first byte of preceding instruction?

a. -115 to 132 bytes

b. -130 to 132 bytes

c. -128 to 127 bytes

d. -115 to 127 bytes

|

25) Which among the category of program branching instructions allow 16 bit address to be specified & can jump anywhere within 64K block of program memory?

a. Long jumps (LJMP)

b. Short jumps (SJMP)

c. Absolute jumps (AJMP)

d. All of the above

|

26) Consider the below mentioned statements. Which among them is /are approved to be incorrect in case of calling instructions of program branching?

a. Absolute Calls instructions specify 11-bit address and calling subroutine within 2K program memory block

b. Long call instructions specify 16-bit address and subroutine anywhere within 64K program memory block

c. Short call instructions specify 16-bit address and subroutine within 4K program memory block

d. All long call and short call instructions specify 11 bit address and the calling subroutine within 16K program memory block

a. Only A

b. B & D

c. A & C

d. C & D

|

27) Match the following instruction mnemonics with their description.

a. CJNE A,direct,rel ------------ 1. Compare immediate to indirect and Jump if not equal

b. CJNE A,#data,rel ------------ 2. Compare direct byte to accumulator and Jump if not equal

c. CJNE @Ri, #data,rel ------- 3. Compare immediate to register and Jump if not equal

d. CJNE Rn, # data rel -------- 4. Compare immediate to accumulator and Jump if not equal

a. A-1, B-2, C-3, D-4

b. A-2, B-4, C-1, D-3

c. A-4, B-3, C-2, D-1

d. A-2, B-4, C-3, D-1

|

28) What is the correct chronological order of the following steps involved in the LCALL operation?

1. Load the value of 16-bit destination address to program counter

2. Increment of the program counter by value '3'

3. Storage of the higher byte of program counter on the stack

4. Increment of the stack pointer by value'1'

5. Storage of the lower byte of program counter on the stack

6. Increment in the value of stack pointer

a. 5, 3, 1, 6, 2, 4

b. 1, 3, 2, 5, 4, 6

c. 2, 4, 5, 6, 3, 1

d. 5, 3, 6, 2, 4, 1

|

29) What is the status of stack pointer for the execution of PUSH and POP operations?

a. It gets post-decremented for PUSH & pre-incremented for POP

b. It gets pre-incremented for PUSH & post-decremented for POP

c. It gets pre-incremented for PUSH as well as POP

d. It gets post-decremented for PUSH as well as POP

|

Answer

Explanation

Related Ques

|

ANSWER: It gets pre-incremented for PUSH & post-decremented for POP

Explanation:

No explanation is available for this question!

|

|

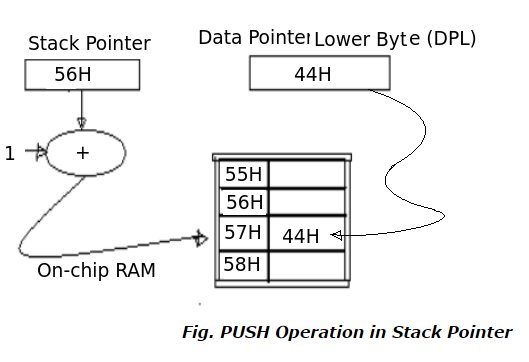

30) What does the following pictorial representation of PUSH operation in the stack pointer indicate among the below stated conclusions/inferences?

a. Stack Pointer is incremented by 2

b. Location 55H in on-chip stack memory gets loaded with 44H

c. Stack Pointer gets initialized by 56H

d. Data Pointer gets loaded with an immediate data 44H which ultimately leads to initialization of stack pointer

a. Only A

b. Only B

c. B & D

d. C & D

|

31) Which instructions contribute to an effective adoption or utilization of stack memory which usually plays a crucial role in storage of intermediate results?

a. ACALL

b. RETI

c. PUSH & POP

d. All of the above

|